CIPERSY RAND

# CENTRAL PROCESSOR UNIT

PAUGRAMMER/OPERATOR

REFERENCE MANUAL

This manual is published by the Univac Division of Sperry Rand Corporation in loose leaf format. This format provides a rapid and complete means of keeping recipients apprised of UNIVAC® Systems developments. The information presented herein may not reflect the current status of the product. For the current status of the product, contact your local Univac Representative.

The Univac Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of hardware or software changes and refinements. The Univac Division reserves the right to make such additions, corrections, and/or deletions as, in the judgment of the Univac Division, are required by the development of its Systems.

UNIVAC is a registered trademark of Sperry Rand Corporation.

Other trademarks of Sperry Rand Corporation appearing in the text of this publication are:

UNISERVO VI C

This manual is published by the Univac Division of Sperry Rand Corporation in loose leaf format. This format provides a rapid and complete means of keeping recipients apprised of UNIVAC® Systems developments. The information presented herein may not reflect the current status of the product. For the current status of the product, contact your local Univac Representative.

The Univac Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of hardware or software changes and refinements. The Univac Division reserves the right to make such additions, corrections, and/or deletions as, in the judgment of the Univac Division, are required by the development of its Systems.

UNIVAC is a registered trademark of Sperry Rand Corporation.

Other trademarks of Sperry Rand Corporation appearing in the text of this publication are:

UNISERVO VI C

UP-4049

Rev. 2

1

# CONTENTS

| CONTENTS                                                                                                               | 1 to 4                              |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 1. INTRODUCTION                                                                                                        | 1-1 to 1-3                          |

| 1.1. GENERAL                                                                                                           | 1-1                                 |

| 1.2. CENTRAL PROCESSOR UNIT CHARACTERISTICS                                                                            | 1-2                                 |

| 2. CENTRAL PROCESSOR OPERATION                                                                                         | 2-1 to 2-24                         |

| 2.1. GENERAL                                                                                                           | 2-1                                 |

| 2.2. EXTERNAL INTERFACE                                                                                                | 2-1                                 |

| <ul><li>2.3. INTERNAL OPERATION</li><li>2.3.1. Interpretation Step</li><li>2.3.2. Execution Step</li></ul>             | 2-3<br>2-3<br>2-5                   |

| 2.4. INPUT/OUTPUT OPERATIONS 2.4.1. ISI Input Mode 2.4.2. ISI Output Mode 2.4.3. ESI Input Mode 2.4.4. ESI Output Mode | 2-7<br>2-12<br>2-12<br>2-13<br>2-13 |

| 2.5. EXECUTIVE CONTROL                                                                                                 | 2-14                                |

| <ul><li>2.6. PROGRAM PROTECTION</li><li>2.6.1. Guard Mode Protection</li><li>2.6.2. Program Protection Modes</li></ul> | 2-14<br>2-15<br>2-15                |

| 2.7. INDEX REGISTERS                                                                                                   | 2-16                                |

| 2.8. MEMORY OVERLAP                                                                                                    | 2-17                                |

| 2.9. RELATIVE ADDRESSING                                                                                               | 2-17                                |

| 2.10. FIXED ADDRESSES                                                                                                  | 2-18                                |

| 2.11. DAY AND REAL-TIME CLOCKS 2.11.1. Day Clock 2.11.2. Real-Time Clock                                               | 2-18<br>2-18<br>2-19                |

PAGE:

Contents

4 - 11

SECTION:

UNIVAC 494

4.4.4. Decimal Arithmetic

CENTRAL PROCESSOR UNIT

UP-4049

Rev. 2

| 4.5. LOGICAL INSTRUCTIONS                                                                        | 4-17       |

|--------------------------------------------------------------------------------------------------|------------|

| 4.6. COMPARISON INSTRUCTIONS                                                                     | 4-20       |

| 4.7. JUMP INSTRUCTIONS                                                                           | 4-21       |

| 4.8. SEQUENCE - MODIFYING INSTRUCTIONS                                                           | 4-25       |

| 4.9. INPUT/OUTPUT INSTRUCTIONS                                                                   | 4-27       |

| APPENDIXES                                                                                       |            |

| A. ABBREVIATIONS AND SYMBOLS                                                                     | A-1 to A-1 |

| B. REPERTOIRE OF INSTRUCTIONS                                                                    | B-1 to B-5 |

| C. INTEGER ADDITION AND SUBTRACTION                                                              | C-1 to C-2 |

| C.1. INTEGER ADDITION                                                                            | C-1        |

| C.2. INTEGER SUBTRACTION                                                                         | C-2        |

| D. EXECUTION TIME OF INSTRUCTIONS                                                                | D-1 to D-3 |

| FIGURES                                                                                          |            |

| 1-1. UNIVAC 494 Central Processor Unit, with Operator's Display Console and Primary Storage Unit | 1-1        |

| 2-1. Central Processor Unit Interface                                                            | 2-1        |

| 2-2. Central Processor Operation, Block Diagram                                                  | 2-4        |

| 3-1. Instruction Word Formats                                                                    | 3-1        |

| 3-2. Register Formats                                                                            | 3-5        |

| 3-3. Arithmetic Operand Formats                                                                  | 3-9        |

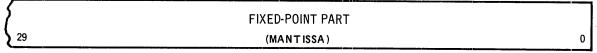

| 4-1. Basic Decimal Arithmetic                                                                    | 4-10       |

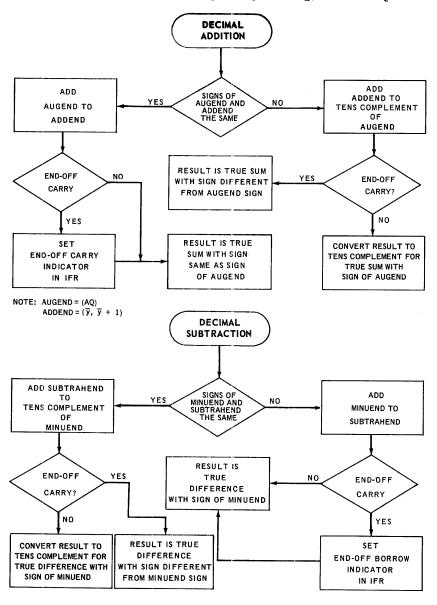

| 4-2. Operation of Typical Return Jump Instruction                                                | 4-23       |

UNIVAC 494

CENTRAL PROCESSOR UNIT

Contents

SECTION:

3

PAGE:

UP-4049 Rev. 2 UNIVAC 494

A-1. Abbreviations and Symbols

B-1. Repertoire of Instructions

D-1. Instruction Execution Time

UP-4049

Contents

A-1

B-1

D-1

PAGE:

## 1. INTRODUCTION

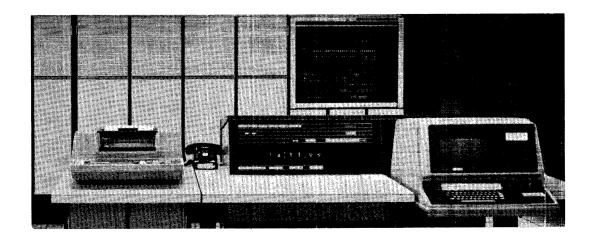

Figure 1—1. UNIVAC 494 Central Processor Unit, with Operator's Display Console and Primary Storage Unit

#### 1.1. GENERAL

The UNIVAC 494 Real-Time System is a large scale information handling system with proven outstanding capabilities in multiprogram operations involving real time communications and data processing activities. As an enhanced successor to the UNIVAC 490 and 491/492 Real-Time Systems, the UNIVAC 494 System combines advanced system hardware and software design concepts and characteristics to fulfill the demands of real time applications while performing background batch processing jobs efficiently. The system is designed around the capabilities of the UNIVAC 494 Central Processor Unit (CPU), shown in Figure 1-1, which is a high speed, powerful digital computing unit. The CPU operates with a flexible framework of interrupts and a comprehensive repertoire of instructions under executive control by the UNIVAC 494 Operating System. The CPU is equipped to handle all of the message, and data transfers and manipulations, including logic, arithmetic, and queue processing called for by the system software; and controls all systems activities and functions. In cooperative interaction with primary storage providing 65 to 131K word capacity, the CPU utilizes a wide variety of peripheral devices and subsystems, including other CPU's and satellite computer systems, in on-site and remote applications to furnish various system configurations and functions according to the specific needs of a particular installation. Inherent system modularity and compatibility in both hardware and software facilitate future additions, expansions, and variations of functions.

Through executive control provided by the system software, the CPU and other hardware components, functioning on a multilevel priority scheme, achieve an optimum program mix in which noncritical programs may be interrupted to permit concurrent execution of real time programs in which time is more critical. All functions associated with selection, initiation, and termination of program elements are also performed under executive control, achieving maximum utility in the system.

Overall system characteristics for both hardware and software are discussed in UNIVAC 494 Real-Time System System Description, UP-4032 (current version).

System software characteristics and logic are discussed in detail in *UNIVAC* 494 Real-Time System Operating System Programmers Reference, UP-7504 (current version).

Characteristics of peripheral hardware components and subsystems are discussed in detail in Systems Programming Library Service publications covering the specific components or subsystems of interest.

#### 1.2. CENTRAL PROCESSOR UNIT CHARACTERISTICS

The CPU provides a variety of features and capabilities which are of advantage to the system user:

- compatibility with an inclusive complement of peripheral subsystems.

- a minimum of 12 input/output (I/O) channels, field-expandable (in increments of four) to a maximum of 24, each of which may carry a complete peripheral subsystem, including I/O devices, communications equipment, or other computers.

- input/output channel operation in the Internally Specified Index (ISI) or Externally Specified Index (ESI) mode for all channels, with the exception of channel 0 which accommodates the operator's console and Day Clock.

- compatibility with UNIVAC 490/491/492 programs and programming techniques.

- read/restore cycle time of 750 nanoseconds.

- interface with a random access ferrite core primary storage (memory) facility having a minimum capacity of 65K 30-bit words (plus a parity bit for each halfword), in two 32K modules which may be cycled independently, expandable in 65K increments to 131K maximum, and with cycle time of 750 nanoseconds and read access time of 400 nanoseconds.

- memory overlap and interleaving capability, permitting the next instruction to be read from memory simultaneously with the reading from or writing into memory of the last operand, for reduced instruction read times.

- relative addressing capability, enabling flexible placement and relocation of programs anywhere within memory.

- buffered input/output, providing capability for program execution concurrently with I/O transfers.

UP-4049

Rev. 2

SECTION:

3

- time orientation to a 24-hour Day Clock and an 18-bit Real-Time Clock, which generate interrupts at specified intervals for program monitoring, loading of instructions, and dealing with contingencies.

- direct arithmetic operations on fixed-point binary single and double precision operands, fixed-point binary coded decimal (BCD) double precision operands, and floating-point binary double precision operands.

- priority control network within the computer I/O logic which determines the order for honoring data transfer requests (function priority) and for responding to system contingencies (interrupt priority).

- response to a flexible and efficient Operating System, comprising the executive routine, utility routines, application packages, assemblers, and compilers.

# 2. CENTRAL PROCESSOR OPERATION

#### 2.1. GENERAL

The UNIVAC 494 central processor unit (CPU) is the prime component of the UNIVAC 494 Real-Time System. The CPU has the responsibility for accepting data and jobs from input/output equipment, queuing and executing jobs in conformance with the demands of a real-time system, and executing and returning the processed results to the system user. The interface between the CPU and the external peripheral equipment is described in this section together with the functional operation and unique processing features of the CPU. These features include the Day Clock and Real-Time Clock, memory overlap and interleaving organization, dual configuration of index registers, and a system of interrupts for control of I/O operations and contingencies.

#### 2.2. EXTERNAL INTERFACE

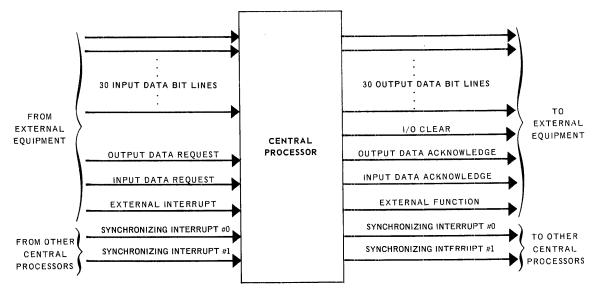

The CPU is designed to operate with a variety of I/O devices and may be equipped with a maximum of 24 I/O channels. A standard subsystem may be tied directly to each channel of the CPU for operating in the Internally Specified Index (ISI) mode, or a communications subsystem may be used between a channel and the I/O subsystem for operating in the Externally Specified Index (ESI) mode (ESI and ISI operations are discussed in subsequent sections of this manual). Each channel has a set of functional lines connected to the external equipment. The external interconnecting lines constitute the external interface, as indicated in Figure 2-1, which implements the exchange of data and control signals.

Figure 2-1. Central Processor Unit Interface

UP-4049

Rev. 2

SECTION:

The I/O controls and their functions are as follows:

The Synchronizing Interrupt signal, which is programmed, causes an interrupt (at the receiving CPU) which transfers control to an interrupt routine. A maximum of two output and two input Synchronizing Interrupt lines may be used per CPU.

The Output Data Acknowledge signal indicates that the CPU has placed a data word on the output word lines.

The External Function signal informs the peripheral device that the output word is a function word rather than a data word. A function word is decoded at the output device to initiate a particular action (read a block of data from magnetic tape, for example). Provision is made within the repertoire of instructions for sending the External Function signal even though an Output Data Request signal (see following paragraph) may not be present.

The Input Data Acknowledge signal indicates that the central processor has stored an input word.

The I/O Clear signal is a master clear instruction transmitted by all I/O channels to the external devices, and is generated when a control at the CPU is manually pressed while the CPU is stopped.

The Output Data Request signal indicates to the CPU that the output device is ready to receive an output data word.

The Input Data Request signal indicates that the input device has placed a data word on the input data lines.

The External Interrupt (EI) signal indicates that the input device has placed a status word on the input word lines, rather than a data word The channel number is immediately stored in a five-bit Interrupt Address Storage register (IASR) and an interrupt is generated transferring control to an executive routine. This routine normally includes an instruction (Store Channel instruction) to store the status word in core memory so that it can be analyzed.

The I/O channels for the CPU are numbered 0-23. Channel 0 can operate in the ISI mode only. The other channels may operate in either ISI or ESI mode and may be changed from ISI to ESI operation or from ESI to ISI operation by a physical change to an I/O printed circuit card. Channel 0 accommodates the operator's console and the day clock. Each group of eight channels (0-7, 8-15, 16-23) can operate in either the compatible mode or in the normal mode. A channel in the normal mode operates at an I/O transfer rate of 555 kHz (kilocycles per second). A channel in the compatible mode operates at a transfer rate of 250 kHz for compatibility with UNIVAC 490 peripheral equipment.

#### 2.3. INTERNAL OPERATION

An instruction requires two steps: the interpretation step and the execution step. During the interpretation step, an instruction word is analyzed to set up the logic circuits for the specific functions called for. During the execution step, the specified functions are performed.

The basic substeps involved in an interpretation step are as follows:

- (1) A 30-bit instruction word is read from memory.

- (2) Portions of the instruction word are analyzed to determine the operand.

- (3) Portions of the instruction word are analyzed to determine the operations to be performed and to condition the logic circuits involved.

The basic substeps involved in an execution step are as follows:

- (1) The operand is read from memory (if required).

- (2) The indicated logic or arithmetic operation is performed.

- (3) The result is written back into memory (if required).

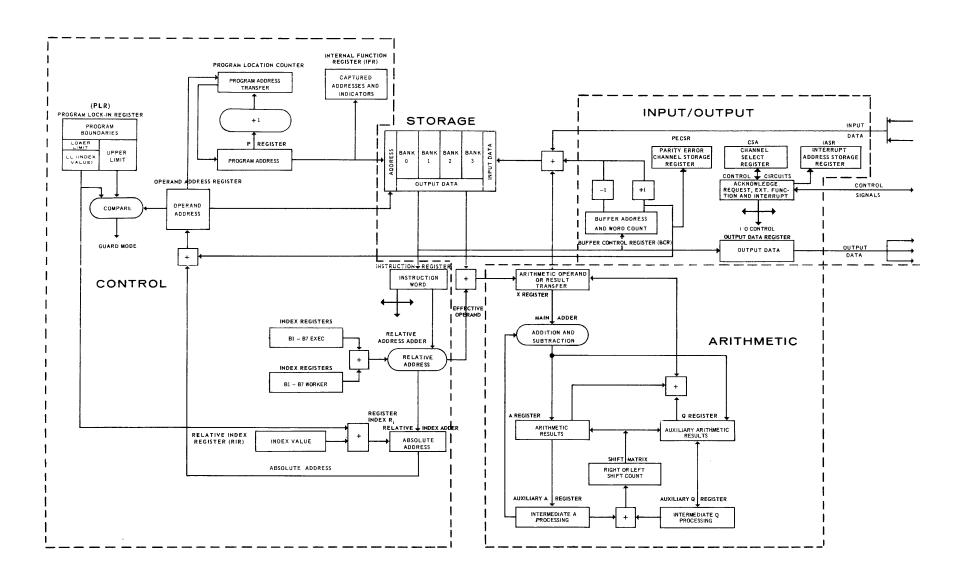

The functional blocks of the CPU which carry out the steps of interpretation and execution steps are shown in Figure 2-2.

#### 2.3.1. Interpretation Step

As part of the initial loading procedure, the address of the first instruction is placed in the Program Location Counter. The contents of the Program Location Counter are transferred to the 17-bit Program (P) register and then to primary storage. The instruction word is read from the indicated address of primary storage into the Instruction register, the word contents are analyzed for operand and function, and the execution cycle is started. Normally, as the execution step starts, the number in the Program Location Counter is increased by 1 and this new value is inserted into the P register. If a skip is indicated during execution, the Program Location Counter will again be incremented by 1 in time to change the contents of the P register before the next interpretation is initiated. If the instruction is a Jump instruction and conditions are satisfied, the new absolute address will be transferred to the P register. (If the instruction is a Repeat instruction, the 17-bit effective address of the instruction is stored in the Internal Function register (IFR) and address transfers to the IFR will be inhibited until the Repeat instruction is completed; if the instruction is a Jump instruction, the 17-bit P value will be stored in the IFR.) Instruction word analysis and conditioning is accomplished as follows:

(1) The basic address contained in the instruction word is added to the contents of an index register, specified by a designator in the instruction word, to form the relative address. Depending upon the activated index register configuration and the index register chosen (see 2.7), the relative address may be either 15 bits or 17 bits.

Figure 2-2. Central Processor Operation, Block Diagram

- \_\_

- (2) The relative address is added to the relative index (R<sub>i</sub>) to form the 17-bit absolute memory address containing the operand. The relative index is either the contents of the Relative Index register (RIR) or the lower boundary or lower lock limit (LL) in the Program Lock-In register (PLR). Bit 27 in the IFR and the b designator of the instruction determine the choice.

- (3) The absolute address is loaded into the Operand Address register and is checked to determine that it lies within the program boundaries.

### 2.3.2. Execution Step

The operand is determined by the 30-bit contents of the Instruction register. In some cases, the operand is part of this instruction word and, if this is so, the operand is sent directly to the X register of the arithmetic circuits, after modification by an index register. In other cases, the instruction word specifies the memory location which contains the operand, and the operand is obtained in the following sequence after the conditioning described in 2.3.1 has been completed:

- (1) The absolute address is sent to the memory and the operand is read from memory into the applicable register.

- (2) The logic circuits, conditioned by timing and execution controls, process the operand, usually retaining the result in one of the arithmetic registers.

- (3) If required by the instruction, the result is also stored in a memory location specified by the instruction word.

All primary storage address references pass through the relative addressing circuits except those references generated by normal sequential operation (including skips) of the P register and those which reference the "fixed" addresses (see 2.10), a group of addresses set aside for interrupt operations. The IFR establishes program protection to ensure that programs do not operate outside the boundaries defined in the Program Lock-In register (PLR), and also establishes Guard Mode to ensure that certain privileged instructions are not executed.

The interpretation and execution steps are essentially limited by the primary storage cycle time. With memory overlap, the last operand of the *current* instruction may be read simultaneously with the *next* instruction, eliminating one memory cycle time between instructions and significantly decreasing the running time required for a program.

The X register is a 30-bit register, handling all communication between arithmetic circuits and primary storage. The register is also capable of furnishing the ones complement (changing 1 bits to 0 bits, and vice versa) of data which it stores.

The accumulator (A register) is the principal arithmetic register and is used in most arithmetic operations. The accumulator is a 30-bit register with complementation capability.

The *Q register* has the same capability as the accumulator. Q assists A in multiplication, division, and logical operations. The A and Q registers are sometimes combined to form one 60-bit register, the AQ register, for double precision and BCD arithmetic operations. Auxiliary 30-bit registers are associated with the A and Q registers, and are used for storage of intermediate results in arithmetic operations.

The shift matrix (K register) enables the contents of the A and/or Q registers to be shifted, at one time, as many positions as required, instead of one bit position at a time.

The Output Data registers hold data on the data output lines long enough to meet requirements of comparatively slow speed I/O devices.

The Buffer Control register (BCR) with one input and one output for each channel minimum, holds the Buffer Control word (BCW) and controls I/O transfers between primary storage buffers and external equipment. The Channel Select register, the Interrupt Address Storage register, and the Parity Error Channel Storage register are concerned with I/O operations; their uses are described in 2.12.

The Internal Function register (IFR) is a 30-bit register used principally to facilitate executive routines. The IFR performs the following functions:

- captures the P register value for Jump instructions;

- captures the relative address of a Repeat instruction and its j designator (see Section 3);

- determines the particular type of program protection to be used;

- indicates overflow or carry for decimal arithmetic;

- specifies whether the executive set or the worker set of index registers is the active index register set;

- determines the bit capacity of the active index register configuration;

- activates one of the two relative addressing modes.

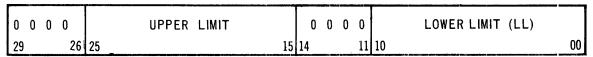

The Program Lock-In register (PLR) defines the upper and lower memory address limits to be used in the particular type of program protection selected by the IFR. The lower limit (LL) may be used as the Relative Index for operands.

The Relative Index register (RIR) is used as a dynamic bias for operand and/or instruction addresses to enable the execution of programs anywhere within memory without modification to these programs. The IFR, PLR, and the RIR are loaded by programmed instructions under executive control.

#### 2.4. INPUT/OUTPUT OPERATIONS

UP-4049

Rev. 2

Input/output operations effect the transfer of data and control signals between the CPU and peripheral equipment. A buffer is a specified number of sequential core storage addresses, starting from a specified address, set aside as required for storing input or output data before it is processed by the CPU or sent to the peripheral device. The 24 (maximum) I/O channels can operate with standard peripheral devices (drums, tapes, printers, etc.) or with multiplexed communication subsystems.

Transfers with multiplexed communication subsystems use the ESI mode. Channel 0 is reserved for, and can only be used through, the operator's console. Transfers with standard peripheral devices use the ISI mode. An ISI channel has one input buffer control register (BCR) and one output BCR (located at the fixed addresses listed in Table 2-1) per channel. For ESI operation, each of the multiplexed I/O devices on a channel is assigned its own input and output ESI location.

All I/O operations are governed by a multilevel priority scale which resolves situations when two or more channels attempt to communicate with the CPU simultaneously. The priority scale uses the fixed priority assigned to each request or interrupt. Function priority determines which of the data requests has the highest priority; interrupt priority determines which of the various I/O interrupts has the highest priority. Function priority and interrupt priority operate independently of each other and each one is a primary level of priority. Both function and interrupt priorities are shown in Table 2-2. Within each of these primary levels there is a secondary level which resolves priority when the same situation exists in two or more channels of the same channel group (15-8, 23-16, and 7-0). In such a case, the highest numbered channel within the group has the highest priority. (The interrupts shown in Table 2-2 are the I/O (conditional) interrupts described in 2.12.)

| ADDRESS | FUNCTION                                 |                               |  |  |  |  |  |  |  |

|---------|------------------------------------------|-------------------------------|--|--|--|--|--|--|--|

|         | 490 MODE                                 | 494 MODE                      |  |  |  |  |  |  |  |

| 000000  | FAULT ADDRESS                            | ILLEGAL INSTRUCTION           |  |  |  |  |  |  |  |

| 000001  | MEMORY PROTECTION                        | PROGRAM PROTECTION OR TIMEOUT |  |  |  |  |  |  |  |

| 000002  | POWER LOSS                               | POWER LOSS                    |  |  |  |  |  |  |  |

| 000003  | MEMORY PARITY BANK #0                    | MEMORY PARITY BANK #0         |  |  |  |  |  |  |  |

| 000004  | MEMORY PARITY BANK #1                    | MEMORY PARITY BANK #1         |  |  |  |  |  |  |  |

| 000005  | BCR PARITY ERROR                         | BCR PARITY ERROR              |  |  |  |  |  |  |  |

| 000006  | I/O DATA PARITY                          | I/O DATA PARITY ERROR         |  |  |  |  |  |  |  |

| 000007  | ,, , , , , , , , , , , , , , , , , , , , | EXECUTIVE RETURN              |  |  |  |  |  |  |  |

| 000010  |                                          | FLOATING-POINT UNDERFLOW      |  |  |  |  |  |  |  |

| 000011  |                                          | FLOATING-POINT OVERFLOW       |  |  |  |  |  |  |  |

| 000012  |                                          | SYNCHRONIZING INTERRUPT #0    |  |  |  |  |  |  |  |

| 000013  |                                          | SYNCHRONIZING INTERRUPT #1    |  |  |  |  |  |  |  |

| 000014  | REAL TIME CLOCK INTERRUPT                | REAL TIME CLOCK INTERRUPT     |  |  |  |  |  |  |  |

| 000015  | DAY CLOCK INTERRUPT                      | DAY CLOCK INTERRUPT           |  |  |  |  |  |  |  |

| 000016  | DAY CLOCK TIME UPDATE                    | DAY CLOCK TIME UPDATE         |  |  |  |  |  |  |  |

| 000017  | REAL TIME CLOCK UPDATE                   | REAL TIME CLOCK UPDATE        |  |  |  |  |  |  |  |

| 000020  | EXTERNAL INTERRUPT CHANNEL 0             | EXTERNAL INTERRUPT ESI        |  |  |  |  |  |  |  |

| 000021  | EXTERNAL INTERRUPT CHANNEL 1             | INPUT MONITOR ESI             |  |  |  |  |  |  |  |

| 000022  | EXTERNAL INTERRUPT CHANNEL 2             | OUTPUT MONITOR ESI            |  |  |  |  |  |  |  |

| 000023  | EXTERNAL INTERRUPT CHANNEL 3             | MEMORY PARITY BANK #2         |  |  |  |  |  |  |  |

| 000024  | EXTERNAL INTERRUPT CHANNEL 4             | EXTERNAL INTERRUPT ISI        |  |  |  |  |  |  |  |

| 000025  | EXTERNAL INTERRUPT CHANNEL 5             | INPUT MONITOR ISI             |  |  |  |  |  |  |  |

| 000026  | EXTERNAL INTERRUPT CHANNEL 6             | OUTPUT MONITOR ISI            |  |  |  |  |  |  |  |

| 000027  | EXTERNAL INTERRUPT CHANNEL 7             | MEMORY PARITY BANK #3         |  |  |  |  |  |  |  |

| 000030  | EXTERNAL INTERRUPT CHANNEL 8             | TEST AND SET                  |  |  |  |  |  |  |  |

| 000031  | EXTERNAL INTERRUPT CHANNEL 9             |                               |  |  |  |  |  |  |  |

| 000032  | EXTERNAL INTERRUPT CHANNEL 10            |                               |  |  |  |  |  |  |  |

| 000033  | EXTERNAL INTERRUPT CHANNEL 11            |                               |  |  |  |  |  |  |  |

| 000034  | EXTERNAL INTERRUPT CHANNEL 12            |                               |  |  |  |  |  |  |  |

| 000035  | EXTERNAL INTERRUPT CHANNEL 13            |                               |  |  |  |  |  |  |  |

| 000036  | EXTERNAL INTERRUPT CHANNEL 14            |                               |  |  |  |  |  |  |  |

| 000037  | EXTERNAL INTERRUPT CHANNEL 15            |                               |  |  |  |  |  |  |  |

| 000040  | INPUT INTERRUPT CHANNEL 0                | OUTPUT BCR CHANNEL 0          |  |  |  |  |  |  |  |

| 000041  | INPUT INTERRUPT CHANNEL 1                | OUTPUT BCR CHANNEL 1          |  |  |  |  |  |  |  |

| 000042  | INPUT INTERRUPT CHANNEL 2                | OUTPUT BCR CHANNEL 2          |  |  |  |  |  |  |  |

| 000043  | INPUT INTERRUPT CHANNEL 3                | OUTPUT BCR CHANNEL 3          |  |  |  |  |  |  |  |

| 000044  | INPUT INTERRUPT CHANNEL 4                | OUTPUT BCR CHANNEL 4          |  |  |  |  |  |  |  |

| 000045  | INPUT INTERRUPT CHANNEL 5                | OUTPUT BCR CHANNEL 5          |  |  |  |  |  |  |  |

| 000046  | INPUT INTERRUPT CHANNEL 6                | OUTPUT BCR CHANNEL 6          |  |  |  |  |  |  |  |

| 000047  | INPUT INTERRUPT CHANNEL 7                | OUTPUT BCR CHANNEL 7          |  |  |  |  |  |  |  |

| 000050  | INPUT INTERRUPT CHANNEL 8                | OUTPUT BCR CHANNEL 8          |  |  |  |  |  |  |  |

| 000051  | INPUT INTERRUPT CHANNEL 9                | OUTPUT BCR CHANNEL 9          |  |  |  |  |  |  |  |

| 000052  | INPUT INTERRUPT CHANNEL 10               | OUTPUT BCR CHANNEL 10         |  |  |  |  |  |  |  |

| 000053  | INPUT INTERRUPT CHANNEL 11               | OUTPUT BCR CHANNEL 11         |  |  |  |  |  |  |  |

| 000054  | INPUT INTERRUPT CHANNEL 12               | OUTPUT BCR CHANNEL 12         |  |  |  |  |  |  |  |

| 000055  | INPUT INTERRUPT CHANNEL 13               | OUTPUT BCR CHANNEL 13         |  |  |  |  |  |  |  |

| 000056  | INPUT INTERRUPT CHANNEL 14               | OUTPUT BCR CHANNEL 14         |  |  |  |  |  |  |  |

| 000057  | INPUT INTERRUPT CHANNEL 15               | OUTPUT BCR CHANNEL 15         |  |  |  |  |  |  |  |

| ADDRESS | FUNCTION                    |                                             |  |  |  |  |  |  |  |

|---------|-----------------------------|---------------------------------------------|--|--|--|--|--|--|--|

|         | 490 MODE                    | 494 MODE                                    |  |  |  |  |  |  |  |

| 000060  | OUTPUT INTERRUPT CHANNEL 0  | OUTPUT BCR CHANNEL 16                       |  |  |  |  |  |  |  |

| 000061  | OUTPUT INTERRUPT CHANNEL 1  | OUTPUT BCR CHANNEL 17                       |  |  |  |  |  |  |  |

| 000062  | OUTPUT INTERRUPT CHANNEL 2  | OUTPUT BCR CHANNEL 18                       |  |  |  |  |  |  |  |

| 000063  | OUTPUT INTERRUPT CHANNEL 3  | 1                                           |  |  |  |  |  |  |  |

| 000064  | OUTPUT INTERRUPT CHANNEL 4  | OUTPUT BOR CHANNEL 19                       |  |  |  |  |  |  |  |

| 000065  | OUTPUT INTERRUPT CHANNEL 5  | OUTPUT BCR CHANNEL 20                       |  |  |  |  |  |  |  |

| 000066  | OUTPUT INTERRUPT CHANNEL 6  | OUTPUT BOR CHANNEL 21                       |  |  |  |  |  |  |  |

| 000067  | OUTPUT INTERRUPT CHANNEL 7  | OUTPUT BCR CHANNEL 22 OUTPUT BCR CHANNEL 23 |  |  |  |  |  |  |  |

| 000070  | OUTPUT INTERRUPT CHANNEL 8  |                                             |  |  |  |  |  |  |  |

| 000071  | OUTPUT INTERRUPT CHANNEL 9  |                                             |  |  |  |  |  |  |  |

| 000072  | OUTPUT INTERRUPT CHANNEL 10 |                                             |  |  |  |  |  |  |  |

| 000073  | OUTPUT INTERRUPT CHANNEL 11 |                                             |  |  |  |  |  |  |  |

| 000074  | OUTPUT INTERRUPT CHANNEL 12 |                                             |  |  |  |  |  |  |  |

| 000075  | OUTPUT INTERRUPT CHANNEL 13 |                                             |  |  |  |  |  |  |  |

| 000076  | OUTPUT INTERRUPT CHANNEL 14 |                                             |  |  |  |  |  |  |  |

| 000077  | OUTPUT INTERRUPT CHANNEL 15 |                                             |  |  |  |  |  |  |  |

| 000100  | INPUT BCR CHANNEL 0         | INPUT BCR CHANNEL 0                         |  |  |  |  |  |  |  |

| 000101  | INPUT BCR CHANNEL 1         | INPUT BCR CHANNEL 1                         |  |  |  |  |  |  |  |

| 000102  | INPUT BCR CHANNEL 2         | INPUT BCR CHANNEL 2                         |  |  |  |  |  |  |  |

| 000103  | INPUT BCR CHANNEL 3         | INPUT BCR CHANNEL 3                         |  |  |  |  |  |  |  |

| 000104  | INPUT BCR CHANNEL 4         | INPUT BCR CHANNEL 4                         |  |  |  |  |  |  |  |

| 000105  | INPUT BCR CHANNEL 5         | INPUT BCR CHANNEL 5                         |  |  |  |  |  |  |  |

| 000106  | INPUT BCR CHANNEL 6         | INPUT BCR CHANNEL 6                         |  |  |  |  |  |  |  |

| 000107  | INPUT BCR CHANNEL 7         | INPUT BCR CHANNEL 7                         |  |  |  |  |  |  |  |

| 000110  | INPUT BCR CHANNEL 8         | INPUT BCR CHANNEL 8                         |  |  |  |  |  |  |  |

| 000111  | INPUT BCR CHANNEL 9         | INPUT BCR CHANNEL 9                         |  |  |  |  |  |  |  |

| 000112  | INPUT BCR CHANNEL 10        | INPUT BCR CHANNEL 10                        |  |  |  |  |  |  |  |

| 000113  | INPUT BCR CHANNEL 11        | INPUT BCR CHANNEL 11                        |  |  |  |  |  |  |  |

| 000114  | INPUT BCR CHANNEL 12        | INPUT BCR CHANNEL 12                        |  |  |  |  |  |  |  |

| 000115  | INPUT BCR CHANNEL 13        | INPUT BCR CHANNEL 13                        |  |  |  |  |  |  |  |

| 000116  | INPUT BCR CHANNEL 14        | INPUT BCR CHANNEL 14                        |  |  |  |  |  |  |  |

| 000117  | INPUT BCR CHANNEL 15        | INPUT BCR CHANNEL 15                        |  |  |  |  |  |  |  |

| 000120  | OUTPUT BCR CHANNEL 0        | INPUT BCR CHANNEL 16                        |  |  |  |  |  |  |  |

| 000121  | OUTPUT BCR CHANNEL 1        | INPUT BCR CHANNEL 17                        |  |  |  |  |  |  |  |

| 000122  | OUTPUT BCR CHANNEL 2        | INPUT BCR CHANNEL 18                        |  |  |  |  |  |  |  |

| 000123  | OUTPUT BCR CHANNEL 3        | INPUT BCR CHANNEL 19                        |  |  |  |  |  |  |  |

| 000124  | OUTPUT BCR CHANNEL 4        | INPUT BCR CHANNEL 20                        |  |  |  |  |  |  |  |

| 000125  | OUTPUT BCR CHANNEL 5        | INPUT BCR CHANNEL 21                        |  |  |  |  |  |  |  |

| 000126  | OUTPUT BCR CHANNEL 6        | INPUT BCR CHANNEL 22                        |  |  |  |  |  |  |  |

| 000127  | OUTPUT BCR CHANNEL 7        | INPUT BCR CHANNEL 23                        |  |  |  |  |  |  |  |

| 000130  | OUTPUT BCR CHANNEL 8        |                                             |  |  |  |  |  |  |  |

| 000131  | OUTPUT BCR CHANNEL 9        |                                             |  |  |  |  |  |  |  |

| 000132  | OUTPUT BCR CHANNEL 10       |                                             |  |  |  |  |  |  |  |

| 000133  | OUTPUT BCR CHANNEL 11       |                                             |  |  |  |  |  |  |  |

| 000134  | OUTPUT BCR CHANNEL 12       |                                             |  |  |  |  |  |  |  |

| 000135  | OUTPUT BCR CHANNEL 13       |                                             |  |  |  |  |  |  |  |

| 000136  | OUTPUT BCR CHANNEL 14       |                                             |  |  |  |  |  |  |  |

| 000137  | OUTPUT BCR CHANNEL 15       |                                             |  |  |  |  |  |  |  |

| I/O FUNCTION PRIORITY          | INTERRUPT PRIORITY               |  |  |  |  |

|--------------------------------|----------------------------------|--|--|--|--|

| Output Transfer Channel 15     | Buffer Control Word Parity Error |  |  |  |  |

| nput Transfer Channel 15       | I/O Data Parity Error            |  |  |  |  |

| 13 or 17 Instruction           | Power Loss                       |  |  |  |  |

| Output Transfer Channels 14-08 | External Interrupt (ESI)         |  |  |  |  |

| nput Transfer Channels 14-08   | Input Monitor (ESI)              |  |  |  |  |

| Output Transfer Channels 23-16 | Output Monitor (ESI)             |  |  |  |  |

| nput Transfer Channels 23-16   | External Interrupt (ISI)         |  |  |  |  |

| Output Transfer Channels 7-0   | Input Monitor (ISI)              |  |  |  |  |

| nput Transfer Channels 7-0     | Output Monitor (ISI)             |  |  |  |  |

| Day Clock Update               | Day Clock Interrupt              |  |  |  |  |

| Real Time Clock Update         | Real Time Clock Interrupt        |  |  |  |  |

| ·                              | Synchronizing Interrupt #0       |  |  |  |  |

|                                | Synchronizing Interrupt #1       |  |  |  |  |

Table 2-2. Input/Output Priority

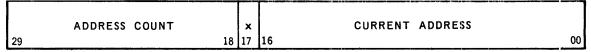

The assignment of buffers is programmed by a buffer instruction (73, 74, 75, or 76), except that an ESI input operation must always be initiated with monitor (75). These instructions activate a buffer and place a buffer control word (BCW) into a BCR. The channel number is obtained from the five-bit Channel Select register (CSR) which was previously loaded by an Enter CSR (7773) instruction. When the buffer is activated, control of I/O transfers is taken over by the BCW so that the CPU is free to process its own program. The BCW defines the first address in the buffer (see Figure 3-2) and specifies the number of consecutive addresses allotted to the buffer. With each transfer, the current buffer address is increased by 1 and the word count is decreased by 1. When the word count reaches 0, the buffer is terminated.

In an input buffer operation, each transfer (updating the BCW and loading the input data into a buffer location) is initiated by the Input Data Request signal. In an output buffer operation, the transfer is initiated by the Output Data Request signal.

When an External Interrupt signal is received on a channel, the channel number is loaded into the five-bit Interrupt Address Storage register (IASR), but the status word on the data lines is not automatically stored. An interrupt is generated and the interrupt routine references the IASR, rather than the CSR, for the channel number. A Store Channel (17) instruction must be used to transfer the status word from the input data lines to primary storage and to send an Input Acknowledge (IA) signal to the subsystem as recognition of the External Interrupt (EI).

Basically, four modes of normal I/O data transfer operation are available:

- ISI mode (input)

- ISI mode (output)

- ESI mode (input)

- ESI mode (output)

11

The ISI modes use fixed addresses (see Table 2-1) for BCR's; the ESI modes can use any memory address as an ESI location (but once specified and wired for a particular I/O device it remains fixed for that I/O device). Actually, the number of ESI buffers which may be active on any one channel is restricted by the amount of primary storage available, the maximum allowable I/O cable length, and the overall transfer rate (which cannot exceed that of the CPU I/O logic).

On ESI input, the peripheral equipment sends an Input Data Request (IDR) along with a 30-bit word in the following format:

| 5, 6, 7 or 8-bit character (right-justified) | ESI address |  |  |  |  |

|----------------------------------------------|-------------|--|--|--|--|

| 29 15                                        | 14 00       |  |  |  |  |

The I/O logic of the CPU uses the ESI address (plus the two bits provided by the MSR) as the ESI location. The BCW is extracted from the ESI location, has its current address (see Figure 3-2) incremented, its word count decremented, and is replaced in the ESI location. Then the I/O logic stores the data on the upper 15 data input lines into the last previous current address (right-justified in the upper 15 bits with zero-fill; the lower 15 bits are undisturbed and may be used for any purpose).

On ESI output, the peripheral device must be connected to both the input and output channels. When the peripheral device sends the computer a request for an output data word, the peripheral device places the address of the corresponding output ESI BCW on the lower 15 bits of the input data lines. I/O logic uses this address (plus contents of the MSR) as the location of the assigned output ESI location. The BCW is fetched, updated, and replaced. Then the word at the last previous current address is sent by way of the 30 output data lines.

Upon termination of an ESI output, the ESI location address is automatically stored in the lower 15 bits of the ISI output BCR for that channel (see Table 2-1). An example of ESI output termination would be: xxxxx 00542 located in address 056. This implies that the peripheral device on position 42 of a communication multiplexer presented ESI address 00542 on channel  $14_{10}$  ( $16_8$ ) along with the Output Data Request (ODR) signal. The data transfer took place, the word count was decremented to 0, and BCR 056 received the ESI location address as an output termination of an ESI channel.

The termination of an ESI input operation differs from the ESI output operation in that the ESI location address is not automatically stored. Upon termination, a monitor interrupt must occur to initiate a subroutine which stores the ESI location address at address Y by means of a Store Channel (17) instruction.

#### 2.4.1. ISI Input Mode

The basic sequence for ISI input is:

- (1) Program activates input buffer for channel specified by CSR (73 or 75 instruction).

- (2) Peripheral unit places data on the 30 input data lines along with IDR signal.

- (3) CPU responds to IDR as soon as possible.

- (4) CPU updates BCW in assigned BCR.

- (5) CPU stores a 30-bit input word at last previous 17-bit current address and sends Input Acknowledge (IA) signal.

- (6) Peripheral unit senses IA signal and drops IDR and data signals.

Steps (2) through (6) are repeated for every data word until the number of words specified by the BCW have been transferred. The channel is deactivated during the transfer of the last word of the buffer.

#### 2.4.2. ISI Output Mode

The basic sequence for ISI output is:

- (1) Program activates output buffer for channel specified by CSR (74 or 76 instruction).

- (2) Peripheral unit sends ODR, indicating that peripheral is ready to receive data.

- (3) CPU responds to ODR when possible.

- (4) CPU updates BCW in assigned BCR.

- (5) CPU reads out data from the last previous current address in the BCR.

- (6) CPU transmits 30-bit data along with Output Acknowledge (OA) signal.

- (7) Peripheral equipment senses OA signal and stores 30-bit data.

- (8) Peripheral equipment drops ODR signal.

Steps (2) through (8) are repeated for every data word until the number of words specified in the BCW have been transferred. The channel is deactivated when the CPU receives the ODR following the last data transfer of the buffer.

#### 2.4.3. ESI Input Mode

The basic sequence for ESI input is:

- (1) CPU activates input buffer for given channel (75 instruction).

- (2) Peripheral unit places data on input lines along with IDR signal.

- (3) CPU responds to IDR signal by updating BCW at location specified in input (plus MSR).

- (4) CPU stores input data at upper half of last previous current address in ESI location and sends IA signal.

- (5) Peripheral unit responds to IA signal by dropping IDR and input data signals.

Steps (2) through (5) are repeated for every data word until the number of words specified in the BCW have been transferred. The channel is deactivated as the last word is read into the CPU.

#### 2.4.4. ESI Output Mode

The basic sequence for ESI output is:

- (1) CPU activates output buffer for given channel (74 or 76 instruction).

- (2) Peripheral unit sends address of output ESI location on lower 15 input data lines along with ODR signal.

- (3) CPU responds to ODR signal when possible.

- (4) CPU updates BCW at output ESI location.

- (5) CPU reads out data from last previous current address in ESI location.

- (6) CPU transmits 30-bit output data along with OA signal.

- (7) Peripheral unit senses OA signal and stores data.

- (8) Peripheral unit drops ODR signal.

Steps (2) through (8) are repeated for every data word until the number of words specified in the BCW have been sent. The channel is deactivated as the last word of the buffer is transferred out. At step (6) when the word count in the BCW is 0, the ESI location address on the lower 15 data input lines will be stored in the output BCR for that channel.

14

#### 2.5. EXECUTIVE CONTROL

Executive control is maintained by a set of routines, the UNIVAC 494 Operating System, which is concerned with selection and execution of worker programs. The executive and other routines control the basic machine facilities and provide for utilization by the worker program within a multiprogram environment. The executive routine is loaded into the CPU as part of the system-initializing procedure, and, from that point on, may be regarded as a programmed extension of the CPU. The routine enforces such basic control as program protection, facility allocation, relocation in memory, etc., and employs essential features of the computer design in effecting its functions.

An executive routine is activated by the occurrence of an interrupt. A special interrupt is generated by the Executive Return instruction enabling a worker program to request service provided by the executive. Interrupt processing is facilitated by the automatic deactivation of RIR and IFR. With IFR inactive, no guard mode or write protection is effective and the executive index registers are active in the 17-bit mode. Executive index registers are used to retain values used in controlling the worker program. With relative addressing inactive, the executive routine can span a 131K memory through the 17-bit index registers. During execution of the interrupt routine, transfers of P to the IFR are inhibited. A Store IFR instruction within the interrupt routine will capture the IFR contents for restoration when the worker is reactivated.

An executive routine required in processing a service request will be activated from an interrupt routine or scheduled for subsequent activation. The interrupt processing is therefore usually limited to a switching or scheduling function so that interrupt processing of input/output, etc., will not be delayed. The interrupt routine will activate RIR, IFR, and release interrupt lockout when control is either switched or returned to the interrupted program. The Enter IFR instruction loads IFR and RIR from successive memory locations Y and Y+1. The relative index established will affect operands of following instructions so that a Jump instruction will normally be direct by an executive index register. Write protection limits established by a previous Load Program Lock-In register instruction and Guard Mode become effective with the activation of IFR. The index register configuration is active prior to the Enter IFR instruction and is effective during the execution step of the next instruction; the interpretation step, however, will be controlled by the new IFR. RIR may be activated independently by IFR by the Enter RIR instruction in special switch situations effected by the executive.

#### 2.6. PROGRAM PROTECTION

Program protection prevents interference between worker programs or program elements. The IFR may select one of three different modes of program protection, or no program protection, to govern the operation of worker programs. (Program protection is automatically disabled for executive routines.) The protection modes are:

- Read and Write Protection with Guard Mode

- Write Protection with Guard Mode

- Write Protection without Guard Mode

15

The Guard Mode is concerned with illegal instructions, and the program protection mode deals with program overextensions, or violations of program limits defined in the PLR.

#### 2.6.1. Guard Mode Protection

The Guard Mode ensures that certain instructions cannot be executed in the course of a worker program. These instructions are: all I/O instructions (13, 17, 62, 63, 66, 67, 73, 74, 75, and 76), and instructions 7760 through 7767, 7770, 7772, 7773, 7774, 7776, and 7777 (instructions restricted to executive routines such as loading of the RIR or IFR). In the Guard Mode, Stop instructions will be executed with any applicable jump, but the stop condition will be inhibited. If the Guard Mode is enabled, any attempt to read the privileged instructions will cause an Illegal Instruction interrupt. The Guard Mode also checks to assure that interrupts are not locked out for a period exceeding 100 microseconds.

#### 2.6.2. Program Protection Modes

Read and Write Protection with Guard Mode uses all the protective features of the Guard Mode and, in addition, will cause a Program Protection or Timeout interrupt if reading, writing, or jumping outside the limits set by the PLR is attempted.

Write Protection with Guard Mode also uses all the protective features of the Guard Mode and will also cause a Program Protection interrupt if writing is attempted outside the limits set by the PLR. However, reading and jumping to any area in primary storage are permitted and are not limited by the PLR.

Write Protection without Guard Mode will cause an interrupt only if writing is attempted outside the limits set by the PLR. Reading and jumping to any location in primary storage are permitted. All instructions in the repertoire can be executed. The Guard Mode is not activated.

Read and/or Write Protection is not applicable on references made by way of the P register. Therefore, a normal P advance or skip outside the limits set by the PLR is not detected. Attempts to reference an instruction outside the lock-in area by a Jump or Execute Remote instruction will be detected and any such reference will not be executed. Also, Read and/or Write Protection is not applicable to I/O data transfers between the CPU and peripheral equipment, since this type of storage protection is effected by Buffer Control words.

#### 2.7. INDEX REGISTERS

UNIVAC 494

CENTRAL PROCESSOR UNIT

Fourteen addressable index (B) registers are available. These registers provide for operand address modification, index codes, counters, and modifier incrementation. These registers are divided into two groups so that each group consists of seven registers. The intention is that one set be used by executive interrupt answering routines and the other set by all other programs.

Only one set of B registers is active at any one time and is selected by the IFR. The executive set is activated when the processor is master cleared and whenever an interrupt occurs. Under program control the executive routine must load the IFR to activate the worker set when leaving the executive routine to enter a worker program. The worker program, in turn, returns to an executive routine by way of an interrupt, thereby activating the executive set.

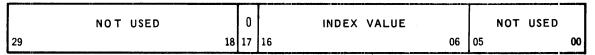

Each set of B registers can operate in one of two modes. In one mode all seven registers will operate as 15-bit registers. In the other mode three registers (B1, B2, and B3) will operate as 15-bit registers and four registers (B4, B5, B6, and B7) will operate as 17-bit registers. To determine which mode is active, a second bit in the IFR is used.

When the CPU is master-cleared or an interrupt occurs, the CPU will operate with the executive set of registers and will have three 15-bit registers and four 17-bit registers. As the executive routine jumps to a worker program, the IFR register is loaded with the appropriate bits to select the worker set of index registers and to select the desired bit mode.

Normal operation for a worker program is the 15-bit length for all index registers, permitting complete access to all data within a 32K memory area. This natural limitation is imposed because 15-bit half-words are normally used for address generation. Any given program including instructions and data will then be contained within a 32K memory area. Using the RIR, the absolute starting address of the 32K area can be varied throughout the 131K memory in increments of 64 words.

The purpose of the 17-bit B registers is to allow a program to reference data outside the 32K limit. The instructions of the program are still limited to the 32K words following the value in RIR, but the data can be stored anywhere in the 131K memory and can then be referenced directly by the program.

When transferring data into and out of the 17-bit B registers, full-word transfers should be used. To enter a 17-bit B register, the lower 17 bits of a 30-bit location are transferred while a full-word store instruction stores the 17-bit value into the lower 17 bits of a 30-bit location with the upper 13 bits cleared to 0's. Half-word transfers into or out of a 17-bit register cause the highest order bits to be set to 0.

Instructions 7741 through 7747 transfer (P-RIR) to B and jump to Y. This is normally a 15-bit value and it can be entered into any B register.

In the instructions which enter and store the worker set of index registers (7771, 7775), a full-word of memory is used; that is, 15 bits are transferred to and from B1, B2, and B3 and 17 bits are transferred to and from B4, B5, B6, and B7 with remaining upper bits written to 0 on a Store instruction. The executive routine uses this instruction whenever it is necessary to save a program environment.

17

#### 2.8. MEMORY OVERLAP

The memory overlap mode capability is achieved by independent operation of the memory banks which make up the primary storage. For a series of one-operand instructions, the time per instruction approaches one memory cycle time, since successive memory references can use alternate memory banks. A manually controlled selector switch (MSR) provides either odd-even addressing or continuous addressing. In the odd-even mode, odd memory references use one memory bank; even memory addresses use another memory bank, minimizing the programming effort necessary for obtaining maximum memory overlap. Odd-even addressing is the normal mode of operation. The continuous mode is used to avoid storage in a particular memory bank (in case of a memory fault, for example). Memory overlap can be obtained in the continuous mode but requires greater programming effort.

#### 2.9. RELATIVE ADDRESSING

Relative addressing permits access to memory locations on the basis of a relative index value,  $R_i$ . Two modes of relative addressing are available for worker programs; interrupt routines do not use relative addressing (or, in effect,  $R_i$  is +0). In the dual relative index mode, either the RIR or the lower limit (LL) of the program boundary in the PLR may be used for  $R_i$  for operand addresses; in the RIR relative index mode, only the RIR may be used for  $R_i$  for operand addresses. In both modes, instruction address memory references shall be relative to the RIR (except for fixed addresses). The dual relative index mode facilitates programming where instructions are located in one primary storage area and operands are located in another. An example of dual indexing is the common subroutine which is entered into primary storage only once but which may operate on data (operands) in several primary storage areas.

Bit 27 of the IFR determines the relative index mode. If bit 27 is 0, the RIR relative index mode is activated; if bit 27 is 1, the dual relative index mode is activated. When an interrupt occurs, the IFR and RIR are deactivated. When the executive routine transfers control to the worker program, the Enter IFR instruction may activate either the dual relative index mode or the RIR mode. The RIR must be entered anew before the jump to the worker program.

In the dual relative index mode, the b designator (see Section 3 for instruction word formats) determines the  $R_i$  as follows:

- If the b designator is 0, 1, 2, or 3, R; is the contents of the RIR.

- $\blacksquare$  If the b designator is a 4, 5, 6, or 7,  $R_i$  is the LL in the PLR.

An Enter B and Jump instruction (774-) or the capture of a relative address by a Return Jump instruction (64 or 65) will store the value of P minus the value of the RIR. Therefore, P values must be relative to the RIR. For example, an executive routine is usually terminated by an arithmetic jump instruction (60) which activates the IFR after the indexing operation. If the jump is direct (the k designator is 0 or 4), any b designator may be used although the dual relative index mode is activated, and P values will be relative to the RIR. However, if the jump is indirect (the k designator is not a 0 or 4) and the b designator is 4, 5, 6, or 7, the RIR would be used to obtain the "jump to" address, the LL would be used to obtain the first worker instruction, and all subsequent values of P would be relative to the LL. In the latter case, the captured relative address (P minus RIR) would not be the true relative address.

#### 2.10. FIXED ADDRESSES

Addresses 000000-0001378 are reserved for entrances to specific interrupt routines and I/O buffer control. Entrance to these audresses is the result of an interrupt or is accomplished automatically during I/O operations. Reference to these addresses is obtained by an original 15-bit address which is modified by the Memory Select register (MSR) to form a 17-bit address. The MSR can be manually set on the maintenance panel to 00, 01, 10, or 11 to select any of the four primary storage modules in the two memory banks. Normally this register is set to 00, and is set to another position usually as the result of a fault in the first memory bank, which setting must be accompanied by a change to the continuous addressing mode instead of the odd-even addressing mode if an MSR setting of 01 or 11 is to be used. Odd-even addressing can be retained if the MSR is set to 10 and the entire second bank is being used.

Relative addressing circuits do not modify fixed address references in the same way as the circuits modify other primary storage addresses. Assignment of fixed addresses is shown in Table 2-1. The MSR is used for bank selection when referencing fixed addresses, for address bias when relative indexing is deactivated, and for bank selection during the initial loading of the CPU.

#### 2.11. DAY AND REAL-TIME CLOCKS

The CPU has two clocks that may be used for program timing: the Day Clock and the Real-Time Clock. The Day Clock is a twenty-four hour clock that records the time of day in hours, minutes, and hundredths of minutes. The Real-Time Clock is an 18-bit counter that is incremented every two hundred microseconds.

#### 2.11.1. Day Clock

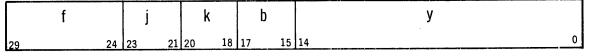

The Day Clock time is stored in primary storage at address 000016 in the following format:

| TENS    | UNITS | TENS  | UNITS | TENS | •       | UNITS |   |   |   |   |   |   |   |   |

|---------|-------|-------|-------|------|---------|-------|---|---|---|---|---|---|---|---|

| HOUR    | 3     | MINU  | TES   | HUN  | DREDTH: | s     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 29 28 2 | 7 24  | 23 20 | 19 16 | 15   | 12 11   | 8     | 7 |   |   |   |   |   |   | 0 |

Time is displayed in hours, minutes, and hundreths of a minute on the operator's console. Every 600 milliseconds, the Day Clock sends a data request signal through the lowest priority input/output channel (channel 00) to update the time contained at address 000016 (bits 08-29). During each input transfer, the data is placed on the 22 upper input data lines. Every six seconds, a Day Clock interrupt occurs, routing the program to main memory address 000015, where the system may start a subroutine conditioned by the time of day.

#### 2.11.2. Real-Time Clock

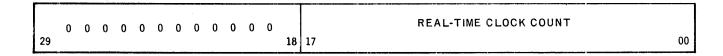

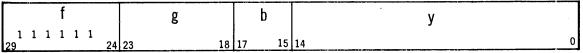

The Real-Time Clock updates the word at the fixed memory address 000017 every 200 microseconds. The word stored at memory address 000017 has the following format:

#### 2.12. INTERRUPTS

Interrupts are signals which temporarily suspend operation of the program being processed and initiate processing of a routine which has an entrance at one of the fixed addresses. Interrupts are generated by programmed instructions, faults, clock operation, or I/O transfer operations.

An interrupt is either unconditional, requiring immediate attention, or conditional, which may not require immediate attention. An unconditional interrupt is never locked out and always locks out conditional interrupts. An interrupt lockout is defined as the condition whereby conditional interrupts may be locked out. This condition can be set up by execution of a Return Jump with j designator of 0 or 1 (SIL) or by processing of any interrupt. The interrupt lockout is in effect until released by a Jump with j designator of 0 or 1 (RIL) or until the machine is mastercleared. There are also temporary I/O interrupt lockouts imposed by the hardware during these instructions. The lockouts are:

- The period between reading of a Repeat instruction from memory and initiation of the first execution of the repeated instruction. This is a period of two memory cycles.

- During all cycles (except the last) of instructions requiring more than one memory cycle. As an example: the Enter B-Worker (7771) requires seven operand references and locks out I/O interrupts for six memory cycles.

UP-4049

Rev. 2

PAGE:

- The execution of an Enter IFR and RIR instruction (7761) locks out I/O interrupts for six memory cycles.

- The execution of an Enter RIR instruction (7766) locks out I/O interrupts for two memory cycles.

When an interrupt sends the program to a fixed address, the P register is not affected by the fixed address. The P register will contain the 17-bit absolute address of the next instruction in the interrupted program, except in the case of a Memory Parity interrupt. Because the Memory Parity interrupt can be generated at any time in the operation of an instruction, the P register will contain either the address of the instruction being performed or the address of the next instruction. It is important to note that if a Guard Mode fault or a Memory Parity fault occurs as a result of an operand read operation for a Jump instruction, the absolute address of the Jump instruction plus 1 will have been captured by the IFR.

The fixed address will usually contain either a Return Jump-Arithmetic or an Enter B and Jump (774-) instruction which captures P minus RIR, a relative address, for use in resumption of the interrupted program. If the relative address is a 17-bit value, the value must be stored in a 17-bit index register, otherwise the two highest order bits will be lost. If the program was interrupted in a Repeat sequence, the 17-bit current relative address of the repeated instruction with the j designator of the Repeat instruction will automatically have been stored in the IFR, together with a designator indicating the Repeat mode. For Jump instruction of the worker program, the 17-bit P value will have been stored in the IFR. On nonjump instructions, the value in the R register is stored in the IFR; the R register value will be a 17-bit absolute operand address or will be an operand dependent upon the operand source of the current instruction.

If an interrupt occurs during a Repeat sequence, address transfers to the IFR are inhibited until the interrupt is processed. The hardware retains this address in the IFR so that a Store IFR (7765) instruction can be executed. The IFR will remain undisturbed until an Enter IFR (7761) instruction is executed. Since the IFR may contain a Repeat designator and address, another Repeat instruction must not be attempted until the Store IFR instruction is executed. (See Repeat instruction, Section 4, for further details.)

#### 2.12.1. Unconditional (Fault) Interrupts

Unconditional interrupts include:

- Memory Parity

- Program Protection or Timeout

- Executive Return

- Test and Set

- Floating-Point Underflow

- Floating-Point Overflow

- Illegal Instruction

#### 2.12.1.1. Memory Parity Interrupt

The Memory Parity interrupt is caused by an error in a read or write operation. As a 30-bit word is written into primary storage, two parity bits (one for each half-word) are written along with the word. As a 15-bit half-word is written into primary storage, a parity bit is automatically generated and written into primary storage along with the half-word. When the contents of a primary storage address (either half-word or full-word) are read, the parity bit(s) are checked to assure that an odd number of bits have not been added or lost from the half-words originally written into memory. As a half-word is written into memory, the other half-word at the same address is automatically checked in a test read operation. Thus, a memory parity error can be detected in a memory read operation of a half-word write operation. A Memory Parity Error interrupt can occur in the interpretation or execution cycle of an instruction, resulting in the "uncertain" P value. Parity errors associated with I/O operations cause conditional interrupts and are discussed further in this section. Parity errors associated with internal transfer of data cause the Memory Parity interrupt, and a different fixed address is assigned to each of the four memory banks.

When a memory parity error occurs, the data is written back into the same address with the parity bit(s). Therefore, further references to the same address will produce another parity interrupt. If the error indicates a malfunction in a memory bank, the fixed locations can be moved to another bank and operation switched to continuous addressing by manual controls.

#### 2.12.1.2. Program Protection or Timeout Interrupt

The Program Protection interrupt is generated when the program protection mode in effect (see 2.6) is violated. A Timeout interrupt is generated if a worker program, running with  $IFR_{21} = 1$ , has been locked-out through a Set Interrupt Lockout (SIL) instruction for more than 100 microseconds.

## 2.12.1.3. Executive Return Interrupt

The Executive Return interrupt is caused by the Executive Return (7754 or EXRN) instruction, which sends the program to a fixed address leading to a routine enabling capture of the P value of the program which is interrupting. The P register will contain the address of the instruction following the EXRN in the program when the interrupt is generated. The IFR will contain a (y+b) value produced by the executive routine.

#### 2.12.1.4. Test and Set Interrupt

The Test and Set interrupt is the result of a Test and Set instruction (7752) which tests bit 14 that is stored at a selected primary storage location. If bit 14 is already set when the test is made, the interrupt is generated and an interrupt routine takes over; if bit 14 is not set, bits 0 through 14 are then set, no interrupt is generated, and the next sequential instruction in the program is executed. The P register will contain the address of the instruction following the Test and Set instruction in the program when the interrupt is generated.

UP-4049

Rev. 2

PAGE:

## 2.12.1.5. Floating-Point Underflow Interrupt

**UNIVAC 494**

CENTRAL PROCESSOR UNIT

The Floating-Point Underflow interrupt is generated when the result of the exponential arithmetic operation has an exponent less than -1024<sub>10</sub> (see arithmetic instructions in Section 4). For multiplication and division, this exponent is also checked in the operands.

#### 2.12.1.6. Floating-Point Overflow Interrupt

The Floating-Point Overflow interrupt is generated when the result of an exponential arithmetic operation has an exponent greater than  $+1023_{10}$  or if exponential division by 0 is attempted, or if any of the exponential operands in multiplication or division has an exponent greater than  $+1023_{10}$ .

#### 2.12.1.7. Illegal Instruction Interrupt

The Illegal instruction interrupt is generated if the Guard Mode is activated and an attempt is made to violate the Guard Mode by privileged instructions. The interrupt is also generated if an attempt is made to execute an instruction with a function code of 00 or 7700. Instructions using unassigned function codes are, in effect, No Operation instructions. No interrupt will be generated; these codes should not be used. If 77xx instructions are attempted with the CPU in the 490 mode, the interrupt will be generated.

#### 2.12.2. Conditional Interrupts

Conditional interrupts are associated with equipment faults, and clock, synchronizing, and I/O operations. Where two interrupts occur simultaneously, channel priority (where applicable) is used as a secondary level in the following order: 15---8, 23---16, 7---0, with channel 15 having highest priority and channel 0 having the lowest priority. Conditional interrupts include:

- BCW Parity

- I/O Data Parity

- Power Loss

- External Interrupt (ESI)

- Input Monitor (ESI)

- Output Monitor (ESI)

- External Interrupt (ISI)

- Input Monitor (ISI)

- Output Monitor (ISI)

- Day Clock Interrupt

- Real-Time Clock Interrupt

- Synchronizing Interrupt #0

- Synchronizing Interrupt #1

## 2.12.2.1. Buffer Control Word (BCW) Parity Interrupt

The BCW Parity interrupt is generated to indicate a parity error in the BCW as it is read from a BCR or ESI location. Every data transfer between a CPU buffer and external equipment involves reading of the BCW, updating the BCW and writing the BCW back into memory. Only during the read cycle can a parity error be detected and the interrupt be generated. If the parity error is detected, the write cycle will write all 0's (parity incorrect) in the BCW. In a buffer input operation, no data word will be stored. The Input Data Acknowledge is sent only on an ESI channel. In a buffer output operation, the data will be sent as all 1's together with the Output Data Acknowledge signal. If the error occurs on an ISI channel, the channel will be deactivated; if an error occurs on an ESI channel, the channel will not be deactivated.

#### 2.12.2.2. I/O Data Parity Interrupt

The I/O Data Parity interrupt indicates a parity error during I/O operations when reading an output data word or writing half-word data (ESI input) as part of I/O operations. Transfers of the data will be completed and channels will not be deactivated. The BCW will be updated and the Output Data Acknowledge signal will be sent.

#### 2.12.2.3. Power Loss Interrupt

The Power Loss interrupt indicates that the input line voltage has dropped below 80 percent of nominal value (which still permits operation). The interrupt routine then has a fixed time of 5 milliseconds to store the status of the program so that when power is restored, the program is supplied with an entry point and can recover in an orderly manner. If the program is operating after this interval, the loss was transient and the program can be resumed with no loss of data.

#### 2.12.2.4. External Interrupt

The External interrupt (EI) is a signal sent from external equipment to CPU together with a status word on the data input lines. The interrupt routine will contain a Store Channel (17) instruction for storing the status word in primary storage. The channel number will automatically be stored in the Interrupt Address Storage register. After the status word has been stored, the Input Data Acknowledge signal will be sent as a result of execution of the Stop Channel instruction.

#### 2.12.2.5. Monitor (Internal) Interrupt

The Monitor interrupt (also termed internal interrupt) occurs when a buffer, activated with monitor, has been either filled or emptied. The interrupt is generated after the write operation (output) or read operation (input) with this one exception: the buffer must receive the next Output Data Request signal before generating the interrupt on an ISI output channel.

#### 2.12.2.6. Day Clock Interrupt

The Day Clock interrupt is generated every 6 seconds, enabling processing operations to be conditioned by the time of day.

## 2.12.2.7. Real-Time Clock Interrupt

UNIVAC 494

CENTRAL PROCESSOR UNIT

The Real-Time Clock interrupt is generated every time the contents of the Real-Time Clock recycle from all 1's to all 0's and may be used for interrupt routines which perform statistical analyses of CPU operations, or for timeouts to prevent program "looping", etc.

#### 2.12.2.8. Synchronizing Interrupt

There are two Synchronizing Interrupt signals: Synchronizing Interrupt #0 and Synchronizing Interrupt #1. The Synchronizing Interrupt signals are sent from one CPU (as the result of a programmed instruction) to another CPU, and cause an interrupt at the receiving CPU. When a Synchronizing Interrupt #0 occurs, the CPU program takes the next instruction from location 0128; if a Synchronizing Interrupt #1 occurs, the CPU program takes the next instruction from location 0138.

#### 2.12.3. I/O Interrupt Registers

The registers which are used by I/O interrupt routines are the Channel Select register (CSR), the Interrupt Address Storage register (IASR), and the Parity Error Channel Storage register (PECSR).

In normal operations, I/O instructions refer to the CSR to determine which channel to activate, deactivate, or test. (The CSR must have been loaded previously by an Enter Channel Select register instruction (7773).)

The IASR contains the number of the channel on which a monitor interrupt signal or an External Interrupt (EI) signal occurs. During the interrupt subroutine, the IASR is used in place of the CSR to specify the channel. When the Store Channel Number (7772) is executed, the number in the IASR is stored. The use of the IASR does not alter the CSR; after the subroutine is completed, I/O instructions again refer to the CSR. The use of the IASR is enabled from the time the interrupt is honored (enter subroutine) until the interrupt lockout is released. It should be noted that if interrupts are locked out under program control, the CSR will be referenced.

The PECSR is used in error routines initiated by a BCR Parity Error interrupt or I/O Data Parity Error interrupt. The channel number of the interrupt is automatically stored in the PECSR. When the Store Channel Number (7772) is executed, the contents of the PECSR will be stored. Within the BCR or I/O Data Parity Error routine, the CSR is used to specify which channel to activate, deactivate, or test.

## 3. WORD FORMATS

#### 3.1. **GENERAL**

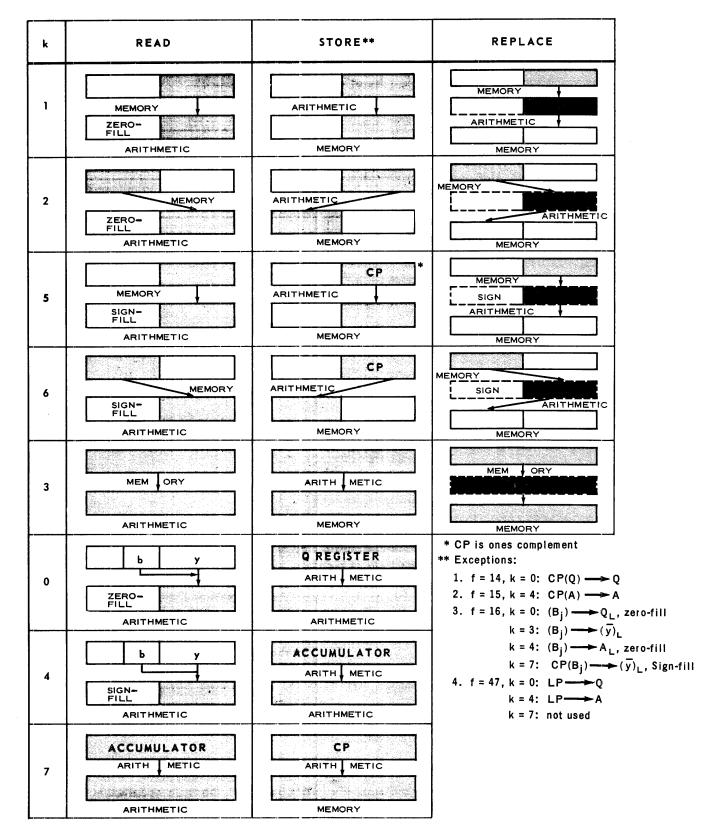

The CPU uses three types of words for internal manipulation: instruction words, register words (the data contained in the registers of Figure 2-2), and arithmetic operands. The variations within each of these types are described in the following paragraphs. Detailed descriptions, where applicable, are furnished in Section 4. (Abbreviations and special symbols used in the text are listed and defined in Table A-1.)

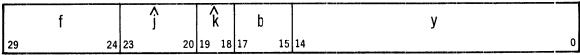

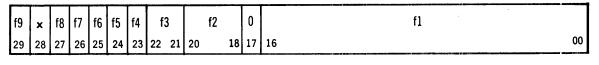

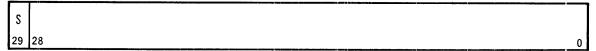

#### 3.2. **INSTRUCTION WORDS**